# Homework 3

(Due date: March 22<sup>nd</sup> @ 7:30 pm)

Presentation and clarity are very important! Show your procedure!

## PROBLEM 1 (75 PTS)

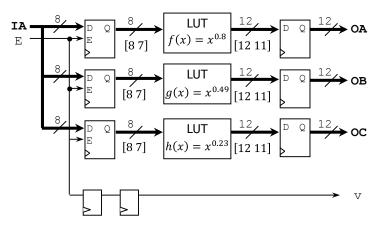

- Implement the following circuit using the LUT approach.

- ✓ Input format: [8 7] (unsigned)

- ✓ Output format: [12 11] (unsigned)

- Pre-compute the LUT values and store them as binary numbers in a text file. Your VHDL code should read the text file.

- The text file should be divided as follows: the first 256 entries for the first function, the second 256 entries for the second function, and the third 256 *f* entries for the third function:

#### SIMULATION

- Create a testbench to test your circuit. The testbench must generate all the possible input cases (from 00000000 to 11111111) and write the output results in a text file. For simplicity's sake, it is suggested that you write three 12-bit words per line (256 lines), where each 12-bit word represents the output of a different function.

- To verify the correct operation of your circuit, compare the text file you are generating on the Simulation with the input text file you created for Synthesis.

- Upload the following files to Moodle (an assignment will be created):

- ✓ VHDL code

- ✓ VHDL testbench

- $\checkmark$  Input and output text files.

## PROBLEM 2 (15 PTS)

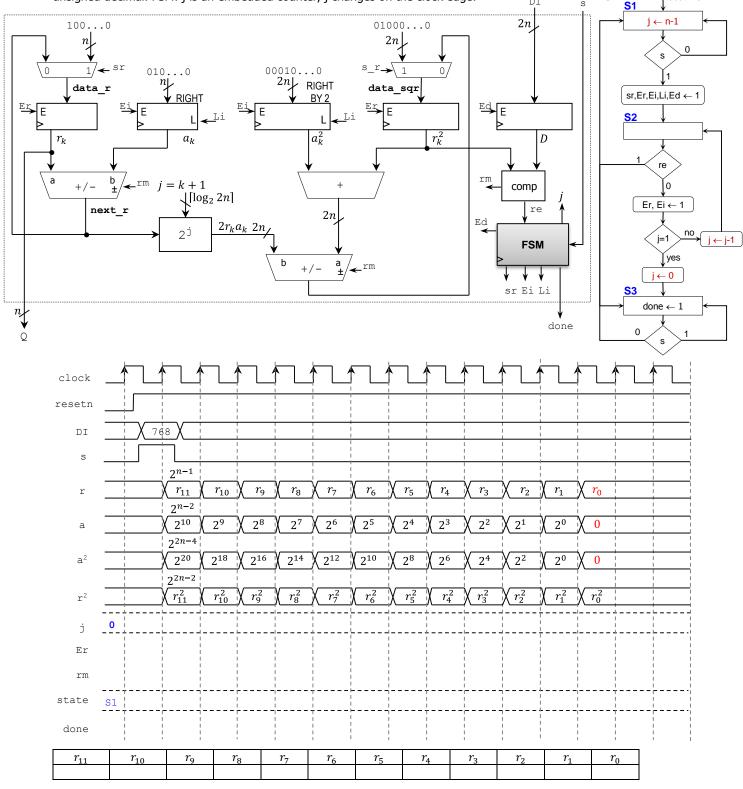

• Complete the timing diagram of the following circuit, which computes integer square root using a binary search approach. n = 12. Note that rm = 1 if  $r_k^2 > D$ , else 0, re = 1 if  $r_k^2 = D$ , else 0. Shift registers: serial input is '0'. The value of D is an unsigned decimal. FSM: j is an embedded counter, j changes on the clock edge. DI S FSM SI  $L^{resetn=0}$

# PROBLEM 3 (10 PTS)

Attach a printout of your Initial Project Report (no more than a page). This report should contain the project title, a brief

project description, and the current status of the project. Use the provided template (Final Project - Report

Template.docx).